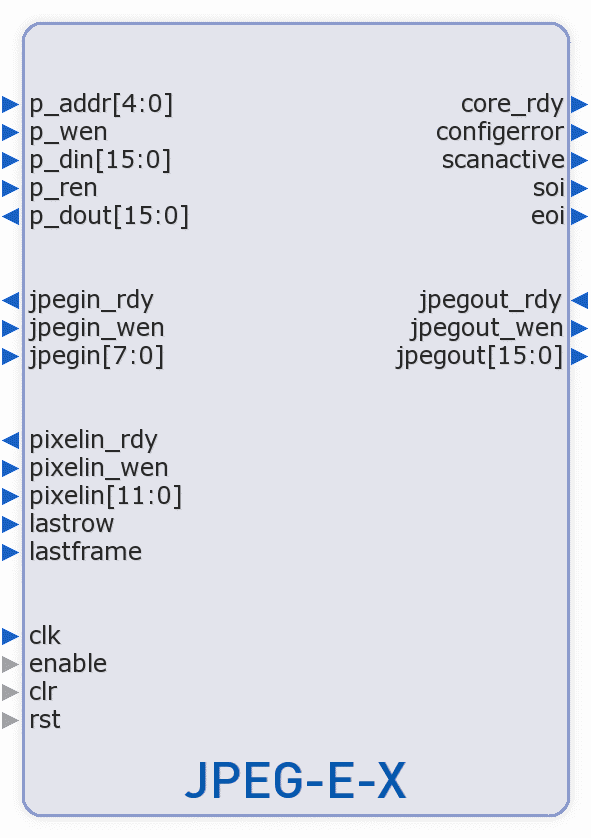

JPEG-E-X

8/10/12-bit Extended JPEG Encoder with Optional Video Rate Control

|

|

|

|

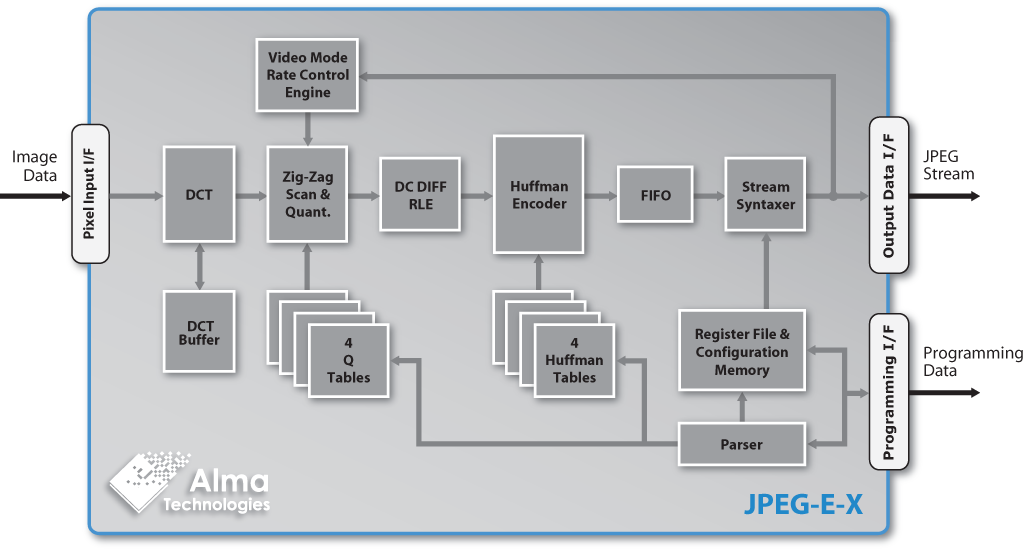

The JPEG-E-X core from Alma Technologies is a standalone and high-performance 8-bit Baseline and 10/12-bit Extended JPEG encoder for still image and video compression applications. Full compliance with the Baseline and the Extended Sequential DCT modes of the ISO/IEC 10918-1 JPEG standard makes the JPEG-E-X core ideal for interoperable systems and devices. The produced JPEG streams can also conform to the Digital Imaging and Communications in Medicine (DICOM) requirements. The JPEG-E-X is available for ASIC or Altera, AMD-Xilinx, Efinix, Lattice and Microchip FPGA and SoC based designs.

In addition to generating standalone Baseline or Extended JPEG streams, the encoder can also produce the (de-facto) standard video payload of many motion JPEG container formats. Furthermore, the bandwidth constrained applications can benefit from the optionally included video rate control block.

The core is designed with simple, fully flow-controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the JPEG-E-X is a reliable and easy-to-use and integrate IP.

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts