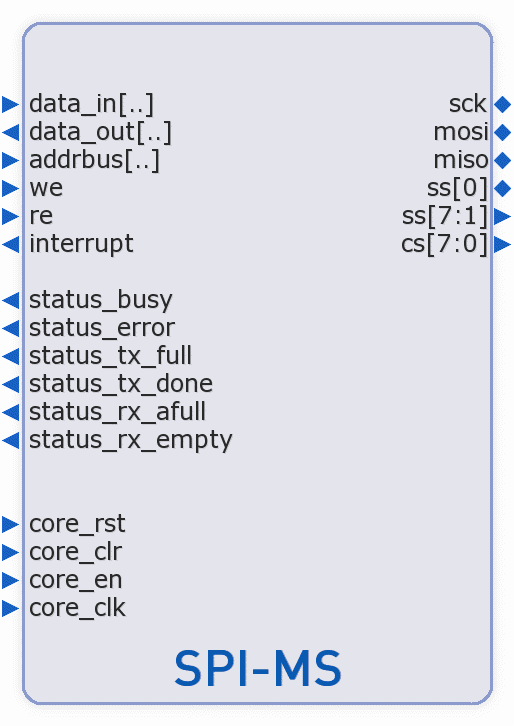

SPI-MS

Master and Slave SPI Bus Controller

|

|

|

|

The Serial Peripheral Interface (SPI) allows high-speed synchronous serial data transfer between microprocessors / microcontrollers and peripheral devices. The SPI-MS core can operate either as a Master or a Slave SPI bus device.

When operating in master mode, the core generates the serial data clock (SCK) and selects the slave device, which will be accessed. The SPI-MS core master is able to generate single-byte or multi-byte frames. The internal data path of the core is configurable between 8,16 or 32-bit width. When using a wider that 8-bit data-path, the core is able to generate partial word transfers, by generating frames with less bytes than the data path width. In this manner the core can transmit a data stream with length that is not a multiple of the data-path width.

When operating in slave mode, another master device on the bus generates the Serial Data Clock and activates the Slave Select input of the core to establish communication. The slave is able to split the received data in partial words, in the case that a smaller than the data-path width frame is received. The slave incorporates mechanisms to reject input noise from the SPI bus, achieving a reliable data reception. Transmitted data are also accurately synchronized with the Serial Clock of the SPI bus.

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts