JPEGLS-E

Lossless JPEG-LS Encoder

|

|

|

|

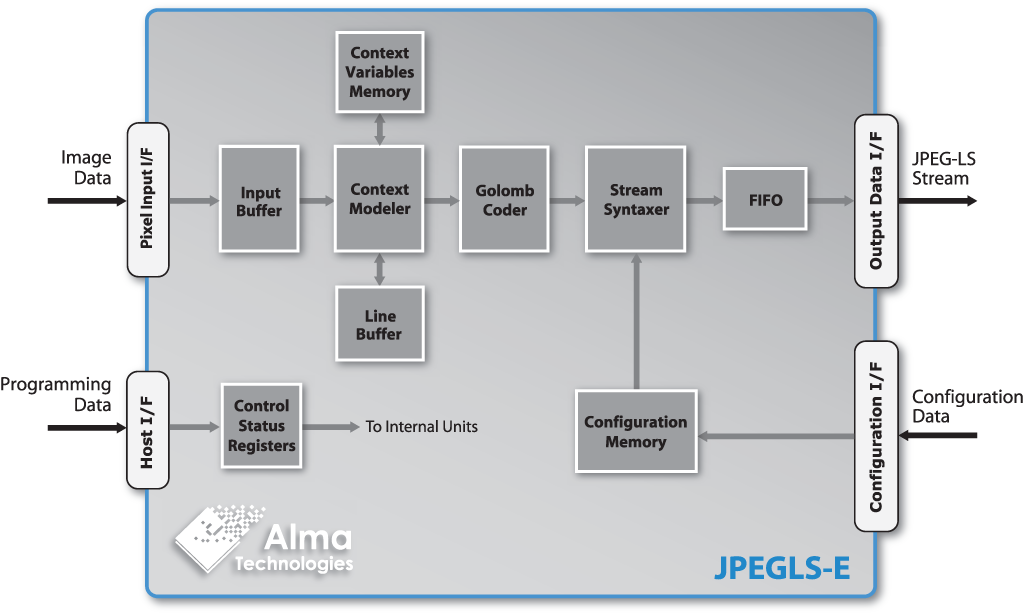

The JPEGLS-E core from Alma Technologies is an ISO/IEC 14495-1 compliant JPEG-LS encoder that offers a very compact, efficient and high-performance solution for up to 16-bit per component numerically lossless image and video data compression. The JPEG-LS standard offers the JPEG 2000 lossless compression efficiency advantage in much more compact silicon footprint and without requiring access to an external memory device. The JPEGLS-E is available for ASIC or Altera, AMD-Xilinx, Efinix, Lattice and Microchip FPGA and SoC based designs.

JPEG-LS was developed to provide a low complexity lossless image compression standard with better compression potentials than Lossless JPEG. The algorithm at the core of JPEG-LS is LOCO-I (Low Complexity-Lossless Compression for Images). It uses a non-linear predictive scheme with rudimentary edge detecting capability, based on the four nearest -causal- neighbours (left, upper left, upper and upper right) and an entropy encoder which uses adaptively selective Golomb-type codes. The low complexity scheme of JPEG-LS is based on the assumption that prediction residuals follow a two-sided geometric distribution and the fact that Golomb-codes are optimal for geometric distributions, thus the modeling and coding units are matching.

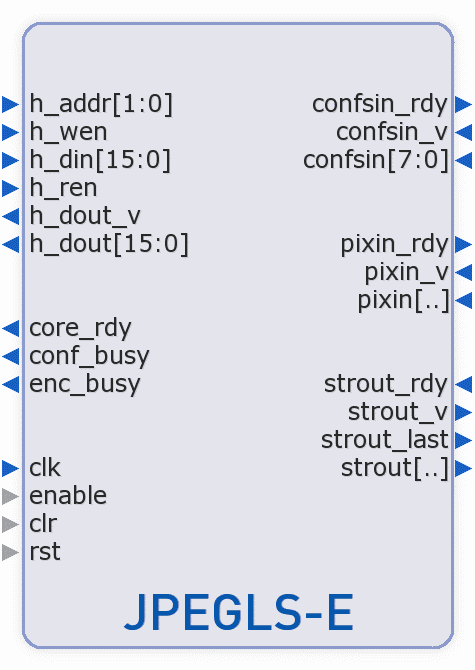

The JPEGLS-E core is designed with simple, fully controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the JPEGLS-E is a reliable and easy-to-use and integrate IP.

The JPEGLS-E is also available in a configuration that adds support for the JPEG-LS NEAR-Lossless encoding mode. The NEAR-Lossless configuration offers higher compression at user defined maximum allowed reconstructed data error, but runs much slower due to a different data-path architecture which has to include feedback loops that cannot be pipelined while maintaining the single clock cycle per input sample processing rate.

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts