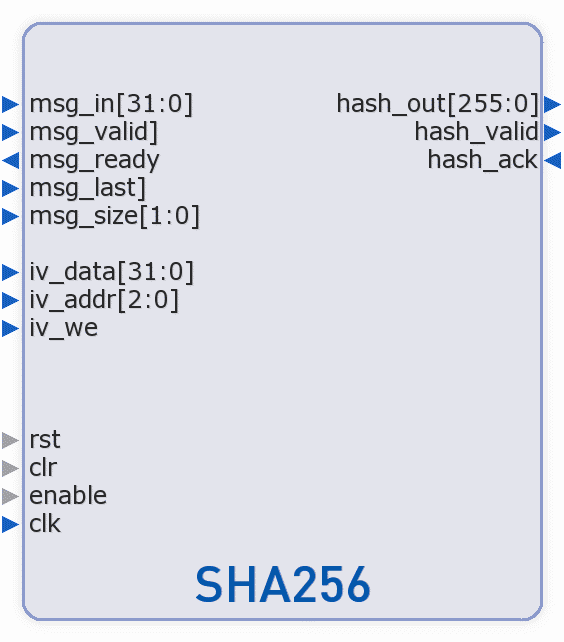

SHA256

SHA-256 IP Core Secure Hash Function

|

|

|

|

The

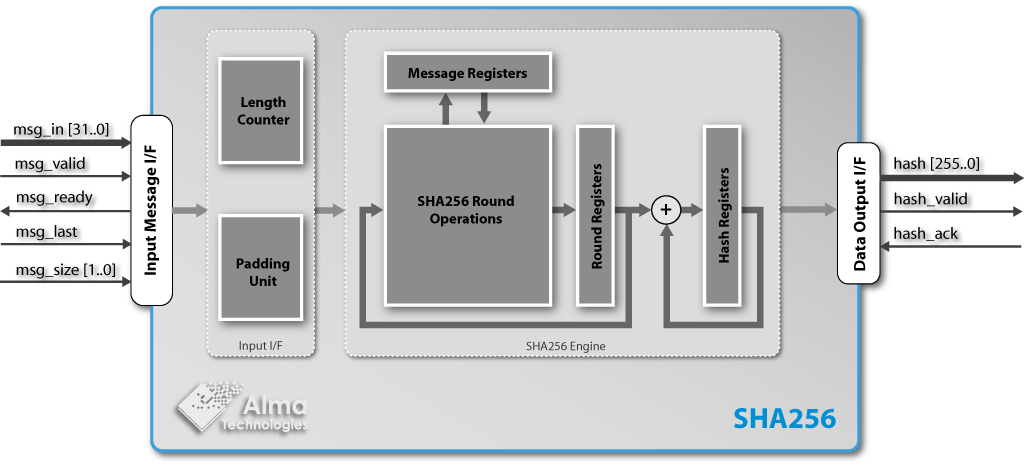

The core is composed of two main units, the SHA256 Engine and the Padding Unit

as shown in the block diagram. The SHA256 Engine applies the

SHA256 loops on a single 512-bit message block, while the Padding Unit splits the input message into

512-bit blocks and performs the message padding on the last block of the message.

The processing of one 512-bit block is performed in 66 clock cycles and the bit-rate

achieved is 7.75Mbps / MHz on the input of the SHA256 core.

The SHA256 core is equipped with easy to use fully stallable interfaces both for input and output. These are designed to permit the user's application to stop the data stream from the core when it is not able to receive data or to stop the input stream towards the core according to data arrival rate.

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts