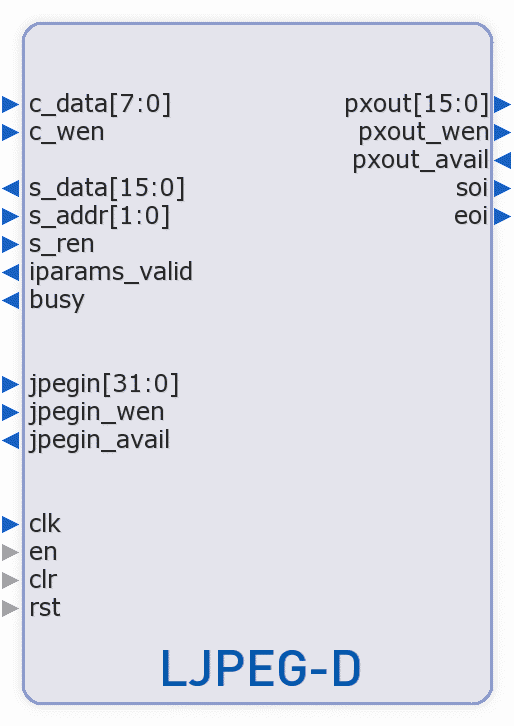

LJPEG-D

Lossless JPEG Decoder

|

|

|

|

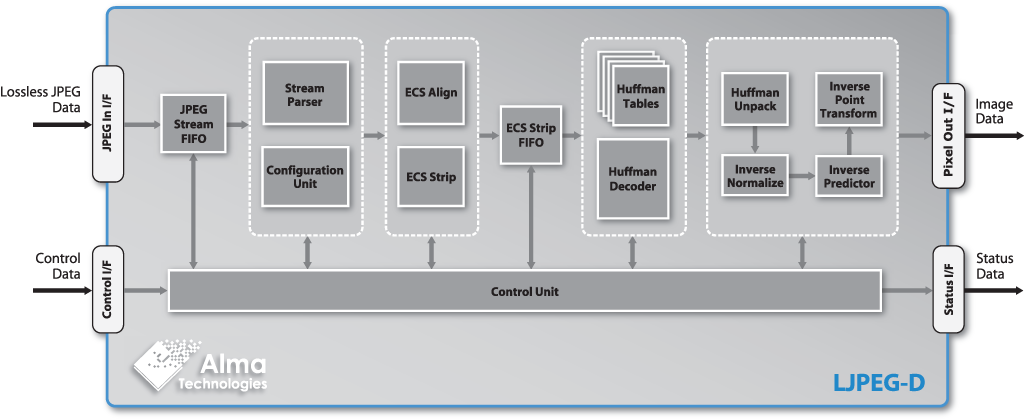

The LJPEG-D IP Core from Alma Technologies is a matching decoder for the Alma Technologies Lossless JPEG Encoder and supports up to 16-bit per component Numerically Lossless decoding. Coupled with the LJPEG-E, the decoder is ideal for image and video compression applications where bit-by-bit accurate reproduction of an image is essential, while the amount of compression needed is very low and the silicon resource usage is critical. The LJPEG-D is available for ASIC or Altera, AMD-Xilinx, Efinix, Lattice and Microchip FPGA and SoC based designs.

The LJPEG-D is based on the spatial (sequential) lossless compression mode (SOF3) of the ISO/IEC 10918-1 JPEG standard. Rather than the Discrete Cosine Transform (DCT) functions used for lossy JPEG compression - which introduce round-off errors - Lossless JPEG employs a predictor function and compresses images by encoding the prediction error with no information loss.

The core is designed with simple, fully flow-controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the LJPEG-D is a compact, reliable and easy-to-use and integrate IP.

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts