CCSDS-122-E

Lossless and Lossy CCSDS 122.0-B-1 Encoder

|

|

|

|

The

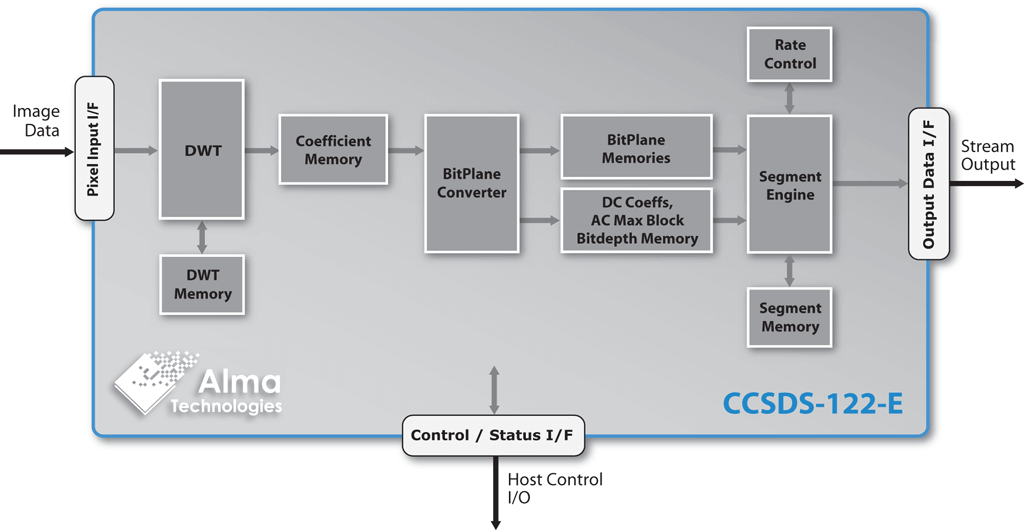

The CCSDS 122.0-B-1 standard fits the compression requirement for a wide range of spaceborne two-dimensional spatial image data. In these applications the requirement is for a scalable data reduction, with the option to use lossless or lossy compression, using a memory-efficient and reduced complexity algorithm that results in a fast, low-power and compact hardware implementation. The Alma Technologies CCSDS-122-E encoder implementation realizes all these expected benefits and supports both lossless and lossy compression with a pixel dynamic range of up to 16 bits.

The CCSDS 122.0-B-1 standard was developed to balance between compression performance and complexity. Similar to JPEG 2000, it utilizes a two-dimensional Discrete Wavelet Transform (DWT) for image data decorrelation. CCSDS 122.0-B-1 uses a 9/7 integer DWT for the lossless compression, while a 9/7 float DWT is also specified for improved lossy compression efficiency, especially at low bit-rates. Both DWT options are available by the CCSDS-122-E core. For complete control by the application of the lossy compression ratio, the CCSDS-122-E includes also the optional rate control functionality that is provisioned by the standard. Compared to JPEG 2000, CCSDS 122.0-B-1 achieves similar lossless and lossy compression efficiency.

The

IP Deliverables

Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

Release Notes, Design Specification and Integration Manual documents

Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

Self-checking testbench environment sources, including sample BAM generated test cases

Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

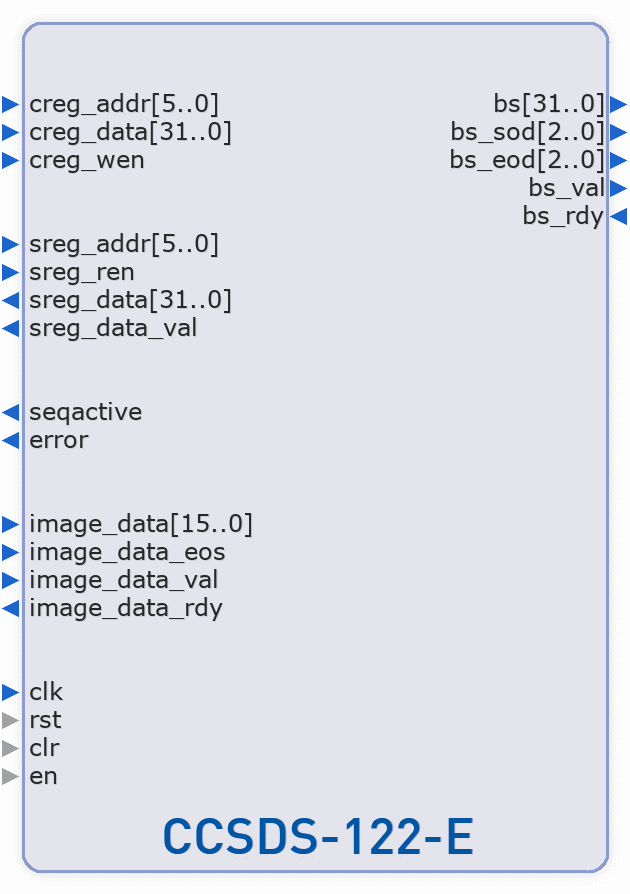

Symbol

Features

CCSDS 122.0-B-1 Compliant, Complete and Standalone Operation

Full compliance to the CCSDS 122.0-B-1 specification

Numerically lossless or lossy compression

Up to 16 bits pixel dynamic range

Both integer and float 9/7 DWT

Integrated rate control

Operation without external memory

CPU/GPU-less, complete and standalone implementation

Smooth System Integration

Full abstraction of the internal implementation and CCSDS122.0-B-1 details from the top level I/O and its operation

Simple, microcontroller like, programming interface

High-speed, flow controllable, streaming I/O data interfaces

Simple and FIFO like

Avalon-ST compliant (ready latency 0)

AXI4-Stream compliant

Designed for both FPGA and ASIC implementations with user configurable architecture before synthesis

Configurable maximum supported image width

Configurable maximum supported pixel dynamic range (up to 8-, 12- or 16-bit)

Configurable DWT filter(s)

Integer only

Float only

Both integer and float

Trouble-Free Technology Map and Implementation

Fully portable, self-contained RTL source code

Strictly positive edge triggered design

D-type only Flip-Flops

Fully synchronous operation

No special timing constraints needed

No false or multi-cycle paths